WP4 - Multi-core hardware architectures and concepts

Objectives

The overall objective of WP4 is developing and evaluating hardware techniques that enable multi-core processors to execute applications with mixed criticalities. The main problem is that the majority of modern architectures have chosen great increases in complexity to deliver relatively small performance improvements. The effect of this has been an increase in the complexity of the design, the verification, and the run-time behaviour to a level where a programmer cannot understand what impact code(s) has/have on run-time behaviour. Under this scenario, mixed criticality systems cannot confidently or efficiently be build, especially ones that are scalable and heavily interconnected.

WP4 will focus on developing hardware architectures and concepts of hardware designs that help satisfy the needs of embedded mixed criticality multi-core systems. The emphasis will be on following issues:

- Freedom from interference of cores with respect to timing and possible failures

- Flexible dynamic techniques to provide fault tolerance and redundancy on demand

- Memory and memory hierarchies suitable for mixed criticality applications

- Flexible concept for interfacing peripheral components and hardware accelerators

- Suitability of existing many-core processor architectures like the TILERA TILE-GX for mixed criticality applications

- Investigation of novel techniques to increase the availability of multi-core systems (i.e. dynamic reconfiguration)

- Investigation of techniques to measure the system’s health status

Work package structure

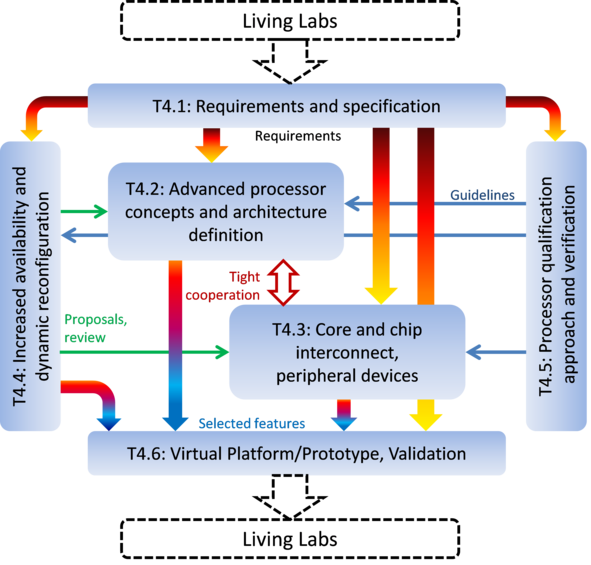

WP4 is organised in six tasks:

Task 4.1 will generate a collection of requirements from the other EMC² technological work packages and the EMC² Living Labs demonstration applications to the multi-core hardware. All requirements will be collected from the aspect of mixed-criticality applications.

Task 4.2 explores novel CPU architectures, interconnect strategies and memory structures with the aim of maximizing the performance of multi-core, multi-memory systems while minimizing area/power increases. Moreover, extensions to the CPU functionality will be provided to support mixed criticalities in a multi-core environment with an optional use of hardware accelerators.

Task 4.3 comprises two major working topics: Interconnect of multiple active system components as well as complete system and the design of peripheral components suitable for mixed criticality applications. Both issues are combined in a single task due to their close relationship and interdependence.

- Interconnect:

The current best way to interconnect large numbers of processors is to use a network (Network-on-Chip at the small scale, Ethernet-style networks at the larger one). If a network is used to interconnect processors either on the same die or between dies or systems, it will need to be timing predicable and to allow Quality of Service (QoS) guarantees for high-criticality applications.

A scalable many-core architecture will be enabled by paying attention to predictability. One of the great benefits of paying attention primarily to application predictability is that doing so greatly improves the ability to write efficient parallel programs, since explicit synchronisation (an overhead) can be reduced or even removed entirely. This would remove a major stumbling block in effectively exploiting parallelism in current state-of-the-art systems. - Peripheral Devices:

The freedom from interference (isolation of threads) cannot be maintained at the level of peripheral components, especially at communication interfaces. Multiple applications executed on a single multi-core chip need to access a common communication interface like an Ethernet, CAN or FlexRay interface. At that time, interference between multiple tasks is unavoidable. Hence, new hardware techniques and software allocation methods need to be developed to deal with this concurrency.

T4.3 will focus on methods and architectures to create dynamically reconfigurable peripherals for hybrid architectures (multicore CPUs plus programmable logic fabric). On one hand, this work will permit to adjust system computing performance in an adaptive manner by dynamically adding and/or removing hardware peripherals. On the other hand, this work will enable the implementation of fault tolerant systems by dynamically auto-repairing damaged peripherals.

The issue of this Task 4.4 is twofold: Challenges regarding analogue components with respect to error and restart situations are investigated. Software-based approaches for redundancy of actions performed by hardware accelerator will be studied.

- Redundancy for hardware accelerators and embedded health monitoring at runtime

The EdkDSP platform can be used as a programmable accelerator for compute-intensive, time-constrained algorithms. Software-based approaches to implement redundancy for accelerated computing will be investigated. Hardware redundancy will also be analysed. Moreover, recognition techniques for sporadical system internal overload situations will be studied. Innovative actions to handle these overload situations will be developed in order to avoid wrong functional behaviour and to increase system availability. - Dynamic Reconfiguration

Reconfigurable microcontroller architectures with support to split on chip resources into subsystems with different levels of independency according to requirements of the applications mapped to them will be evaluated. New proposals will be studied to be integrated in the demonstrator platforms.

The state-of-the art in verification of multi- and many-core systems is not sufficiently advanced. The huge complexities that arise from interaction of processors, the interconnects themselves and between memory accesses, all in the context of mixed criticality applications, require the development of new verification methodologies that extend the state of the art beyond the current SoC level. Development includes both formal and simulation-based approaches and combinations of these to arrive at a methodology that is effective and efficient in practice and paves the way to certification.

In Task 4.6 the proposals of the WP4 tasks will be implemented as demonstrators for showing and validating their suitability and efficiency. The demonstrators will be realized as simulations (virtual platforms) or as FPGA prototypes.

Virtual platforms can range from simulations of CPUs, to simulators of multiprocessor SoCs (MPSoCs) through to complete ECUs which can be run as an alternative to hardware in the loop development approaches. These offer simulation speeds orders of magnitude faster than RTL simulations and debugging/monitoring capabilities greater than development boards.

In parallel, an FPGA MPSoC together with a suitable FPGA prototyping platform will be developed. The resulting prototype will be used in selected Living Labs for demonstration purposes.