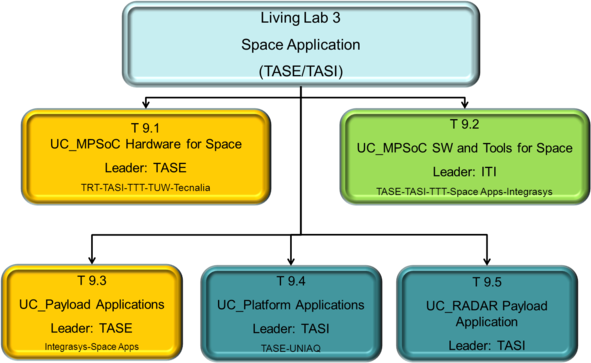

LL3 - Space application

Objectives

Design of data handling systems and data processing systems for space applications is currently introducing technologies quite new to the space market as multi-core processors, hierarchy of cache memories or SoC. In the space business, the SoC are newcomers that are entering the market at an extremely slow speed, especially when compared with the promised advantages that such systems may bring in terms of performances improvement. The main reason for this small adoption ratio is the criticality of the space borne systems and the associated validation and certification procedures. There is a lack of methodologies and tools to support the exploitation of these new technologies in the scope of systems which are compliant to the strict non-functional requirements of criticality, safety, timeliness, security and reliability peculiar to the space applications.

The target of this living lab is to proof the validity of different Multi-Processor Based system architectures and a related development methodologies and tool chains, opening new application domains to the use of multicores. Each of these applications will be presented as a Use Case conceived to show the new functionalities that can be achieved through the usage of the EMC² proposed techniques and architectures. Each Use case will be clearly targeted to a final product application and, therefore, it must be guaranteed not only compliance with the functional requirements, but also, to non-functional requirements currently peculiar to space applications, pushing forward these non-functional requirements pointing to the larger flexibility provided by heterogeneous systems.

Work package structure

Living Lab Space Applications comprises five use cases:

This Use Case will be focused on the multicore architectures presently available in the market and the possibilities of implementing them in Space Worth systems that are capable of withstanding the space environment and that can follow the stringent design rules specified for Space equipment. The objectives of this Use Case 9.1 are:

- Develop and validate MPSoc solutions for the high reliability applications required in the Space Domain

- Develop and validate High Processing capacity solutions based on the MPPB architecture already proposed by ESA

- Develop a MCSoc architecture for Microcontroller based solutions such as planetary rover motor control units

- Migrate and adapt to space the ACROSS architecture developed in the automotive domain

The core of the proposed architectures will be the processor selected by the European Space Agency for the next generation of data handling systems for space applications. The proposed architectures will take into account the final application, splitting in four main lines:

- High reliability

- High Processing Capacity

- MCSoC for Space and

- TTEthernet.

The ability to properly reuse scarce resources on a spacecraft can determine the success or failure of a mission. The important advances in hardware of the last decade are slowly, but inevitably, being adopted in the space domain: multiprocessor (LEON4), reconfigurable hardware, etc. The challenge is now how to exploit all the capabilities of this new hardware without jeopardizing the certification process. The more static and fixed is the behavior of the system the easier is to certificate it. Unfortunately, the ideas of dynamic reconfiguration or workload balance always plays against the certification due to the difficulty to cover and analyze all the cases. This living lab will analyze and address the potential blocking issues that may prevent the use of the new HW both at the HW level and in the interaction with the software development cycle of highly critical systems.

Different OSs and tools will be evaluated and checked against the space standards in order to define an MPSoC toolset that guarantees the space worthiness of the different Software developed. The tool-set developments will also comprise TTEthernet tool plug-ins and tool extensions in order to connect the specific space related tool plug-ins to the standard TTEthernet tool environment. Furthermore specific drivers will be provided in the area of TTEthernet based end-systems supporting Sysgo Pike OS. These toolsets will be evaluated and recommended for the rest of the Use Cases.

This Use Case will implement the EMC² solutions to three typical satellite payload applications in order to assess the performance improvements that the MPSoC technologies can bring into the satellite business. In the same way, this Use Case will provide feedback to the developers of architectures and tools in order to adapt the different developments to the specific needs of satellite payloads. In order to provide results as close as possible to the final applications, the three proposed developments will be targeted at building breadboards of actual satellite equipment with requirements derived from existing missions.

The objectives of this Use Case are:

- Apply the MPSoC architectures for high capacity video processing in the design and validation of a new Integrated Video Processor for Earth Observation Instruments

- Develop a next On board Processor Input section based on the MPPB architecture for data demodulation and decoding

- Develop and validate High Processing capacity solutions based on the MPPB architecture already proposed by ESA

- Develop a MPSoC multiprocessor platform for Secure satellite Communications to be applied in ground stations and satellite Hubs

The three applications to be covered in this Use Case are

- MPSoC Video Processor for Earth Observation Instruments

- MPPB for On Board Data Processing and

- Multiprocessor platform for Reliable Space Communications.

The discipline of on board data handling systems design for space applications is currently facing the challenge to integrate a number of new technologies like multi-core processors with hierarchy of cache memories and MMU, hypervisor and TSP operating systems. If these new technologies provide engineers with the tools to cope with applications of complexity currently unworkable, there is a lack of methodologies and tools to support the exploitation of these new technologies in the scope of systems with strict criticality and safety requirements.

The objectives of this Use Case are:

- Spacecraft Platform Avionics with Mixed Criticality Applications on Multicore Processor. Apply the MPSoC architectures in the Spacecraft Platform Avionics. This application will pay special attention to solve the mixed criticality issues that appear in this environment, as the overall platform management presents various levels of criticality and dependability both at software and hardware level.

- Multiprocessor platform for OBDP (On Board Data Processing) for ISL (Inter Satellite Link) application for navigation solution: Develop an Multiprocessor platform for OBDP (On Board Data Processing) for ISL (Inter Satellite Link) application for navigation solution.

- Multicore architecture for low cost hardening of On Board Data Handling Units: Apply self healing architectures and techniques in the development of a main controller device of a platform Remote Terminal Unit in order to obtain hardness through the usage of low cost devices empowered by reconfiguration and gentle degradation techniques.

Modern Monitoring-&-Forecasting Geoscience-Services as well as Governmental-Operations for the Homeland Protection (HP) demand an ever increasing performance of remote-sensing capabilities from space. Accordingly the evolution of Spaceborne Radars (SBRs) proceeds at small, yet steady, steps towards improvements in terms of Mission Aspects, Signal Processing Techniques, Payload Architectures, and related (possibly blue product line) Enabling Technologies. More specifically future SBR Payloads requirements are evolving in strict correlation to the trends in specific aerospace and electrical engineering fields sprouting towards flexible, modular, interoperable, and cost-effective payloads subsystems.

The key concept for this strategy relies on tactics aimed at exploiting advanced Analysis, Simulation, and Breadboarding activities for Knowledge Aided (KA) Designs and Distributed High-Performance-Extreme-Computing (HPEC) digital architectures based on large and fast Shared-Memories. In particular Multicore-Microprocessors should be aimed either at Job-Level Parallelism via multiple processors running independent activities i.e. Multiple-Instructions-Multiple-Data (MIMD) or at Parallel Processing via multiple processors running simultaneously the same activity i.e. Single-Instruction-Multiple-Data (SIMD).

This application paves the way for such SBR challenges providing proof-of-concept of the aforementioned Distributed HPEC architecture based on a Large-Shared-Memory taking as a reference a preliminary and scaled study-case for Onboard Raw-Data Acquisition for novel Multi-Channel Synthetic Aperture Radar (SAR) High-Resolution-Wide-Swath (HRWS) modes comprising Elevation Digital Beamforming (DBF) processing, Azimuth Multi-Channel processing, and Block Adaptive Quantization (BAQ) processing on dummy digital inputs.