Newsletter no. 4

## Editorial

Welcome to the 4<sup>th</sup> EMC<sup>2</sup> Newsletter which will provide an impression on selected EMC<sup>2</sup> topics and intermediate project results. In this issue we will focus on:

| I.    | Joint Project Conference and Exhibition with French         |    |

|-------|-------------------------------------------------------------|----|

|       | Systematic Cluster                                          | 1  |

| II.   | EMC2 design environment integration for mixed-              |    |

|       | critical CPS                                                | 2  |

| III.  | Mechanisms for dynamic runtime environments and             |    |

|       | services - highlights and cooperation                       | 5  |

| IV.   | Automotive Applications with Service Oriented               |    |

|       | Architecture (SOA)                                          | 9  |

| ٧.    | EMC <sup>2</sup> use case "Highly automated driving"        | 11 |

| VI.   | EMC <sup>2</sup> use case: "Design and Validation of Next   |    |

|       | Generation Hybrid Powertrain"                               | 14 |

| VII.  | COTS Multicores in Avionic Applications                     | 15 |

| VIII. | FPGA PARTIAL RECONFIGURATION IN SPACE                       |    |

|       | APPLICATIONS                                                | 17 |

| IX.   | EMC <sup>2</sup> "Internet of Things" use cases             | 19 |

| Х.    | EMC <sup>2</sup> use case: "Video Surveillance for Critical |    |

|       | Infrastructure"                                             | 21 |

| XI.   | Developing safety & security co-engineering methods         |    |

|       | for cyber-physical systems – Windows of Opportunity         |    |

|       | for Standardization                                         | 22 |

| XII.  | EMC <sup>2</sup> Workshops and Special Sessions at renowned |    |

|       | Conferences in 2016: CPS-Week, SAFECOMP,                    |    |

|       | Euromicro DSD/SEAA                                          | 27 |

|       |                                                             |    |

#### I. JOINT PROJECT CONFERENCE AND EXHIBITION WITH FRENCH SYSTEMATIC CLUSTER

The 2016 EMC<sup>2</sup> project conference was organized together with the Systematic Cluster following the main goals:

- Collect feedback of different users.

- Share experiences and best practices.

- Inform the French ecosystem on the guidelines of the project.

The joint event took place on Sept. 28 at Préfecture des Paris et d'Île-de-France in Paris. The morning session was organized by the Systematic Cluster by four working groups: Digital Trust & Security, Systems Design & Development tools, Automotive & Transport and Smart Cities. Video recordings of all presentations are available via Youtube:

- <u>Introduction and Agenda</u> (Gérard Poirier, Dassault Aviation)

- EMC2 (presentation of Werner Weber, Infineon)

- <u>Embedded France</u>: The French Embedded Cluster (Cedric Demeure, VP at Thales & President of Embedded France)

- <u>S3P project</u> (presentation of Eric Bantegnie Leader of S3P project – VP at Ansys)

- Innovation through collaborative projects : From an innovation project to a product, software, digital technologies and business

- Presentation of Proxima et Contrex projects

Impressions from the EMC<sup>2</sup> conference and exhibition, Sept. 28, 2016, Paris

The afternoon session was organized by EMC<sup>2</sup> building a bridge to other related projects. Both sessions were accompanied by EMC<sup>2</sup> demonstrations showing best practices in mixed-criticality, multi-core embedded

Newsletterno, 4

systems design and realization. More than 200 persons visited the demonstrations at the conference. In addition, the presentation sessions were made available remotely, where further 158 persons watched either the live streaming or the video on Youtube.

**Presentations:**

- EMC<sup>2</sup> A platform project on embedded microcontrollers in applications of mobility, industry and the internet of things (plenary talk, Werner Weber, Infineon Technologies)

- The S3P project Smart, Safe and Secure Platform • (Eric Bantegnie, Ansys)

- PROXIMA Improving measurement-based timing • analysis through randomisation and probabilistic (Francisco analysis J. Cazorla. Barcelona Supercomputing Center)

- CONTREX Design of embedded mixed-criticality • CONTRol systems under consideration of EXtrafunctional properties (Kim Grüttner, OFFIS)

#### Demonstrations:

- art2kitekt A modelling and analysis tool for aerospace domain (Sergio Sáez, ITI)

- ZG3D Parallelization of an industrial inspection • system (Juan Carlos Pérez, ITI)

- Multicore application design using embedded • Procedure Call Library (eRPC) (Petr Lukas, Marek Novak, NXP CZ)

- A Native segregation of multiple virtual networks over only one physical link (Philippe Ravier, P. Aristote, SILKAN)

- A Benes Based NoC Switching Architecture for Mixed Criticality Embedded Systems (Steve Kerrison, UoBR)

- A Hardware Platform for distributed Radar Processing (Martin Terry, Zuhal Clarke, IFXUK)

- A Safe, Secure and Adaptive Mixed-Criticality System (Youssef Zaki, Detlef Scholle, ALTEN)

- What is this thing called OSLC? (Johnny Öberg, KTH)

- Modelling Support for a Linked Data Approach to Tool Interoperability (Jad El-khoury, KTH)

- Space Platform Applications (Dario Pascucci, TASI); demonstration

- m2cpp exploring multi-cores by generating c++ from MATLAB (Hans Petter Dahle, Fornebu)

- Object detection on FPGA : Signal, image and video processing (Marin Musil, Petr Musil, BUT)

- Interference Measurement and Mitigation Means on Multi-Core COTS processors (Jimmy Le Rhun, Thales)

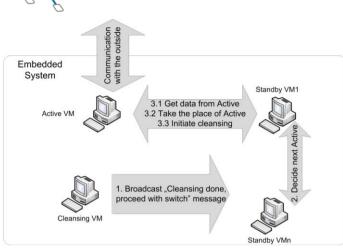

- Blind hypervision to protect virtual machines (Olivier Heron, CEA); demonstration

- Many-Core Architecture Integration Experiments in a Representative Avionics Environment (Moha Ait Hmid, CEA)

- Safe Dynamic Resource Allocation in Mixed-Critical Systems (Paul Debrulle, CEA)

- Integrated Specification, Design and Documentation flow for Mixed Criticality Embedded Systems (Pfeiffer, Magillem)

- VITRO Vision Testing for Robustness (Oliver Zendel, AIT)

- Virtualization-based security and fault tolerance (Zhendong Ma, AIT)

- WEFACT System qualification and certification (Erwin Schoitsch, AIT)

#### **EMC2** DESIGN ENVIRONMENT INTEGRATION FOR II. **MIXED-CRITICAL CPS**

Frank Oppenheimer Mladen Berekovic **OFFIS**

TU Braunschweig

Adam Kostrzewa TU Braunschweig

Haris Isakovic. TU Vienna

The concept of cyber-physical system has been introduced to unite and bind all individual disciplines involved in the whole process from early design to product implementation of industrial or consumer applications. The concept connects the digital and the physical world through a series of mutually dependent interdisciplinary steps.

## Newsletter no. 4

Once completely independent system components are now co-designed, modeled and simulated to increase the overall performance and efficiency. In EMC<sup>2</sup>, we are covering the whole spectrum of interdisciplinary activities in the CPS design process, from specification in WP1 to the mechanical actors interacting with the physical environment in different use cases (WP7-WP12).

The efficient development of mixed-critical CPS requires a seamless interplay between different layers in the design stack. The hardware layer must provide a reliable electronic architecture supported through services in the run-time system that provide a hardware abstraction layer while allowing to segregate functional and extrafunctional behavior. Based on these mechanisms, the application layer must support the explicit modelling of the intended behavior including its criticalities and communication interrelations.

In EMC<sup>2</sup> these layers are being addressed in three corresponding workpackages (WP). WP2 provides modelling and design languages at application layer, which allow the designers to specify the application tasks including their timing behavior, communication relations and different criticalities. Tools for analyzing, mapping and optimizing the scheduling of mixed critical applications support the designers. With the support from an efficient run-time environment, applications can be executed on modern hardware platforms. The temporal and spatial segregation of different tasks needs sophisticated run-time mechanisms.

WP3 develops a large set of such technologies supporting various advanced hardware platforms. The implementation of mixed-critical applications on multi-core hardware platforms is a specific challenge. Only when the hardware platform provides support for virtualization and predictable communication and timing behavior, the run-time system and thus the application can be implemented according to its requirements.

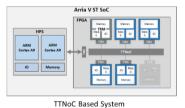

In order to enhance mechanisms and architectures for the run-time environments (RTE) in WP3, we firstly conducted evaluation of the existing platforms with respect to the support for mixed-critical systems, security techniques as well as safety and real-time properties. Later technologies targeting WP3 goals were proposed including mechanisms for virtualization, hypervisors and monitoring. The main objective was to adapt existing systems to the increasing application system dynamics without losing effectiveness or efficiency. Partners considered on-chip architectures as well as off-chip solutions. Consequently, selected platforms from WP4 were analyzed in WP3 with respect to the dynamic support for Quality-of-Service guarantees targeting different aspects of the design as interconnect communication or resource allocation. For instance, we analyzed the IDA-NoC belonging to the SoCRocket framework (WP4) and proposed the control layer allowing decoupling mechanisms for admission control from the data flow control in the system. Similarly, we proposed mechanisms for the dynamic re-configuration for on-chip networks applicable, which is the part of the Arria V SoC platform (WP4). The proposed extensions were evaluated with respect to the safety requirements, overheads and possible performance benefits. One of the evaluation goals was to build a basis for future extensions of mapping and analysis tools considered in WP2, e.g. art2kitect, to allow easier and flexible system design and implementation which could support feasibility check for a particular mechanism on a selected platform.

WP4 explores and extends existing hardware architectures, concepts and platforms. It covers different levels of abstraction in communication, from an on on-chip and inter-chip communication, to a component to component communication, or a system to system communication. Moreover, WP4 is working on integration of peripheral devices, validation and verification, and dynamic reconfiguration capabilities in hardware.

In the design process for CPS, a hardware platform is often co-designed with the rest of the system. This enables a tighter integration between individual components. A hardware platform is a set of hardware components connected together such that they provide a specific set of functionalities. It can be implemented completely using COTS components (e.g. EMC2-DP, XILINX ZYNC, AURIX), or custom made using programmable logic (e.g., SoC Rocket, Time-triggered MPSoC, MCENoC). The advantages and flaws of one or the other approach depend on the specific set of requirements for each application. These are not always exclusively related to functional requirements of the system, but also with other conditions i.e., certification, cost, or time to market. The design process is highly

## Newsletter no. 4

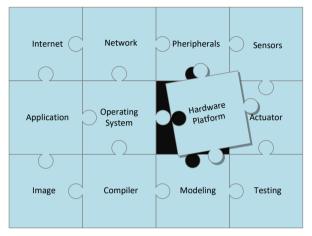

influenced by instruments and tools used in the process and these have a huge impact on system integration. A standalone hardware platform without an efficient runtime environment or software modeling approach is a small part in a highly complex puzzle (Figure 1). This is why the unified design and implementation process between different disciplines in both digital and physical part of the system is necessary.

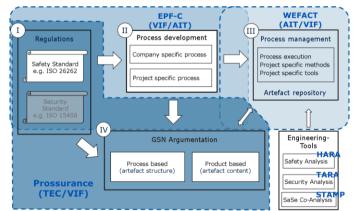

Figure 1: The design environment "puzzle"

Tools for hardware design and configuration need to reach out towards tools and mechanisms on higher levels of abstraction (e.g., on application layer) and provide information necessary for seamless integration. A tool like this can be used to map and optimize applications on specific platforms. Furthermore, integration of custom hardware using programmable logic is more complex and requires significantly more design efforts. We are identifying tools and mechanisms that are able to bridge this gap and provide efficient way to use custom hardware in a domain and application independent fashion.

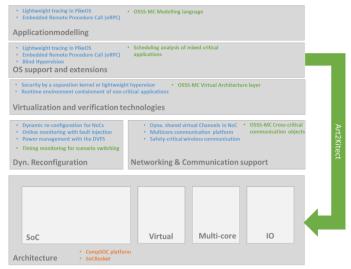

During the first half of the EMC2 project, we were focusing on developing the necessary modeling languages, mechanisms and technologies. In the second half, the attention shifts more towards the integration and interplay of these technology building blocks. Rather than keeping this effort on a theoretical basis, we decided to aim at the practical integration of at least some major results of WP2, WP3 and WP4. Figure 2 depicts a design environment, which contains individual contributions from all three workpackages. While every design environment must provide solutions to all relevant activities, the particular needed technologies depend on the requirements of the use-case application.

Figure 2: Practical example of a design environment

Without a practical example, this approach would remain a theoretical concept with no true evidence of being applicable in practical product development. In order reduce the significant design effort of such a use-case study, we have chosen the well-understood internal usecase from WP2. The multi-rotor application contains all significant components of a mixed-critical application and is available in full source code. There is already reference implementation using significant parts of WP2 modelling approach and has been implemented using a COTS (XILINX ZYNC SoC) hardware architecture and standard run-time systems.

We are currently applying the major WP2 mapping and analysis framework (art2kitect). This allows modeling the application tasks with its abstract timing requirements and a rather coarse grain representation of potential hardware platform alternatives (see Figure 3).

The aim is here to model different variants of hardware platforms developed in WP4, which are supported by mechanisms coming from WP3. We want to demonstrate that our design environment can address those different hardware platforms (see Figure 4) as developed in WP4.

| Task                   | mming<br>del<br>red) Obje                                        |                              | erformanc<br>ask set                     | e-critical Saf                         | ety-eritical task                                          |                                                                          | S2                                                                |                                               |

|------------------------|------------------------------------------------------------------|------------------------------|------------------------------------------|----------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|

| ed-0<br>sour           | Critical<br>ce Mod                                               | lity<br>del                  |                                          | Task<br>Contair<br>Runtir              | Tasi<br>Contai<br>ne Model                                 |                                                                          |                                                                   |                                               |

|                        |                                                                  |                              |                                          |                                        |                                                            |                                                                          |                                                                   |                                               |

| PM                     | <b>A</b> M                                                       | SA Sys                       | stem Analysis                            | CG                                     |                                                            |                                                                          |                                                                   |                                               |

| PM                     | RTA Ma                                                           | anual A                      | llocation                                | _                                      |                                                            |                                                                          |                                                                   |                                               |

| PM                     | RTA Ma                                                           | anual A                      | llocation                                | cc                                     |                                                            |                                                                          |                                                                   |                                               |

|                        | RTA Ma                                                           | anual A                      | llocation                                | _                                      |                                                            | a w                                                                      | Cale model 🗸 S                                                    | etings 💽                                      |

|                        | RTA Ma                                                           | anual A                      | llocation                                | _                                      |                                                            |                                                                          | dule model 👽 8<br>hange units for all                             | etings 🕨                                      |

|                        | RTA Ma<br>Response                                               | anual A                      | llocation                                | _                                      |                                                            |                                                                          | hange units for all                                               | etings 🕨                                      |

| 0                      | RTA Ma<br>Response                                               | anual A                      | llocation                                | _                                      | /<br>Response Time (us)                                    | c                                                                        | hange units for all                                               | etings 🖡                                      |

| Cpl<br>Flow            | RTA Ma<br>Response                                               | anual A                      | llocation<br>alysis for Par              | titioned Systems                       |                                                            | Ci<br>inalysis performed. P                                              | hange units for all                                               | etings 🖡                                      |

| Cpl<br>Flow            | RTA Ma<br>Response                                               | e Time An<br>Priority        | llocation<br>alysis for Par              | titioned Systems                       | Response Time (us)                                         | Ci<br>inalysis performed. P<br>Deadline (us)                             | hange units for all<br>rocessor workload<br>Period (us)           | etings                                        |

| CpL<br>Flow<br>Flow_Pe | RTA Ma<br>Response                                               | Priority                     | Ilocation<br>alysis for Par<br>wcet (us) | titioned Systems<br>Biocking Time (us) | Response Time (us)<br>1,235.2                              | Cl<br>nalysis performed. P<br>Deadline (us)<br>30,000                    | hange units for all<br>rocessor workload<br>Period (us)           | etings<br>telds un<br>is feasible<br>Feasible |

| CpL<br>Flow<br>Flow_Pe | RTA Ma<br>Response<br>11<br>Task<br>nod-3000                     | Priority<br>0<br>2           | Ilocation<br>alysis for Par<br>wcet (us) | titioned Systems<br>Biocking Time (us) | Response Time (us)<br>1,235.2<br>1,235.2                   | Cl<br>nalysis performed. P<br>Deadline (us)<br>30,000<br>30,000          | hange units for all<br>rocessor workload<br>Period (us)<br>30,000 | etings                                        |

| CpL<br>Flow<br>Flow_Pe | RTA Ma<br>Response<br>11<br>Tesk<br>mod-3000<br>Leit<br>nos-2000 | Priority<br>0<br>2<br>0      | WCET (US)                                | Blocking Time (us)                     | Response Time (us)<br>1,235.2<br>1,235.2<br>1,229          | Ca<br>nalysis performed. P<br>Deadline (us)<br>30,000<br>30,000<br>2,000 | hange units for all<br>rocessor workload<br>Period (us)<br>30,000 | etings Leids un<br>Isifeasible                |

| CpL<br>Flow<br>Flow_Pe | RTA Ma<br>Response<br>11<br>Task<br>Mod-3000<br>Lait<br>Mod-2000 | Priority<br>0<br>2<br>0<br>0 | WCET (US)<br>6.2<br>1,114                | titioned Systems<br>Blocking Time (us) | Response Time (us)<br>1,235.2<br>1,235.2<br>1,229<br>1,114 | Ca<br>outysis performed. P<br>Deadline (us)<br>30,000<br>2,000<br>2,000  | hange units for all<br>rocessor workload<br>Period (us)<br>30,000 | etings                                        |

Figure 3: Top: application Modell in OSSS-MC, Bottom: Timing analysis in art2kitect

In the design process, we want to prove that the application model can be developed independent of the hardware platform using appropriate run-time environment mechanisms. The main achievement of this activity will be to show the integration of contributions from three different workpackages into a seamless design environment for a complete application.

#### III. MECHANISMS FOR DYNAMIC RUNTIME ENVIRONMENTS AND SERVICES - HIGHLIGHTS AND COOPERATION

Adam Kostrzewa, TU Braunschweig

The broad objective of WP3 is to enhance the European knowledge in mechanisms and architectures for the existing run-time environments (RTE) that are able to support mixed-critical systems, security techniques, safety and real-time properties. Technologies include mechanisms such as virtualization, hypervision and

Newsletter no. 4

| LEON3<br>Processor       | Debug Support<br>Unit | JTAG Debug<br>Link | On-Chip<br>Memory       | High Bandwidth<br>Peripherals |

|--------------------------|-----------------------|--------------------|-------------------------|-------------------------------|

| AHB<br>AHB<br>Controller | Memory<br>Controller  | IDA NI             | AHB/APB<br>Bridge       |                               |

| PROM                     | I/O SDRAM             | IDA NOC            | Interrupt<br>Controller | Low Bandwidth<br>Peripherals  |

Bus Based System

4x4 homogenous NoC System

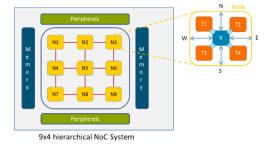

Figure 4: Architecture alternatives

monitoring, which need to be adapted to the increasing application system dynamics with no loss in effectiveness and minimal loss in efficiency. In this article, we present the broad overview of the conducted work using as examples demonstrators presented during the review meetings and conferences. Additionally, we show from the perspective of WP3 the technology transfer and cooperation with WP4 ("Multi-core hardware architectures and concepts") and WP2 ("Executable Application Models and Design Tools for Mixed-Critical, Multi-Core Embedded Systems").

Among the main challenges of the WP, the most important one was to propose solutions applicable to different RTEs, i.e. solutions that are independent from

### Newsletter no. 4

specific hardware and communication networks and, instead, rely on well-defined interfaces. Although the existing RTEs are domain specific, the underlying principles show many similarities. Therefore, in the EMC<sup>2</sup> project, partners of WP3 exploit these similarities to simplify portability and safety, as well as cross domain usage and integration of systems, including technology transfers between WP2, WP3 and WP4. In the last four deliverables, which were submitted in the scope of WP3, almost 80 inputs were gathered proposing nearly 40 mechanisms and improvements. New RTE functions are developed and deployed driven by the strategy and methodology based on the evaluation, cooperation and validation.

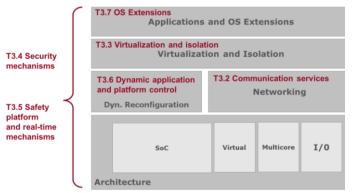

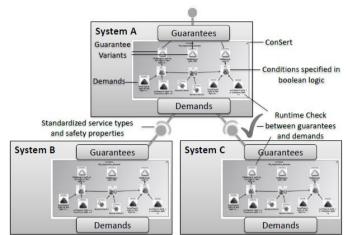

WP3 is split into six technology clusters grouping the mechanisms in different tasks based on their purpose and scope: communication services (T3.2), virtualization and isolation (T3.3), security mechanisms and services (T3.4), safety platform and real-time mechanisms (T3.5), dynamic application and platform control (T3.6) and OS support functions (T3.7). The coverage of the underlying system architecture by different technology clusters is presented in Figure 5, which depicts a broad overview of the undertaken effort.

Figure 5: Connection between tasks in WP3 and the SoC architecture originating from WP4

Some of the clusters are targeting specific layers of the system, whereas others propose inter-layer solutions. Moreover, many of the introduced mechanisms offer complex and mature solutions with particular elements (aspects) developed in the independent tasks. The general architecture chart follows the structure proposed in WP4, for easy mutual identification of concrete problems and solutions in both WPs as well as direct and indirect partner cooperation. The direct cooperation

considers transfer and application of the mechanisms in architectures from WP4, as done for instance by TTTech and their mechanism for dynamic network re-configuration in. Similarly, Infineon proposed the microcontroller firmware compliant with standard ISO26262 for fast and bug-free development targeting the AURIX chip, applied in WP4 for failure safe operation and simplified development. The indirect cooperation considers the information exchange as well as evaluation of application possibilities between the involved partners. Some of the mechanisms in WP3 directly evaluate architectures considered in WP4 e.g. the CompSOC platform proposed by TUE relying on Xilinx Microblaze processors as one of the components. As WP3, contrary to WP4, considers also off-chip solutions not every mechanism can be directly transferred between WPs, however many of them can serve as inspiration for the solutions as many of the problems repeats across the domains.

In the next section, we present the overview of the conducted work using as examples four mechanisms developed in the scope of the WP3 which were presented as demonstrators during the review meetings and conferences.

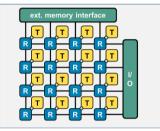

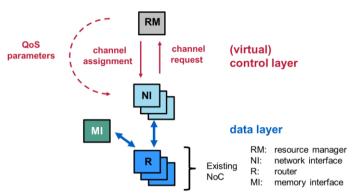

#### Dynamic sharing of Virtual Channels in Network-On-Chip (TUBS)

TUBS proposed in T3.6 an alternative approach for providing efficient service guarantees in NoCs for mixedcritical real-time systems. It concentrates mainly on the virtualization and isolation layer from Figure 6. Its aspects, however, consider also dynamic reconfiguration and networking. The mechanism combines the global scheduling for the end-to-end guarantees, with the local arbitration performed in routers. TUBS introduces scheduling modules, called resource managers (RMs), with which applications have to negotiate their accesses to interconnect. Synchronization is achieved using control messages and a dedicated protocol. RMs conduct a global, priority based scheduling and grant transmissions access to the NoC for a predefined amount of time. This allows exclusive access to the NoC, hence reducing blocking and decreasing the size of necessary buffers in routers. Moreover, it supports sharing of the same VC between transmissions with different criticality levels while preserving service guarantees. This can be used to decrease the number of required VCs in a system or to

increase the number of hosted applications. The efficiency of the solution derives from work-conserving priority aware scheduling which directly addresses requirements of transmissions with different criticality levels.

*Figure 6: Structure of the SoC system with the global and dynamic arbitration introduced by TUBS*

The average utilization is additionally improved through dynamic budgeting. This allows to drastically reduce the average latencies (i.e. temporal over-provisioning) compared to other time-triggered architectures. Therefore, RMs allow to overcome the drawbacks of previously described approaches through reducing hardware overhead compared to non-blocking routers as well as temporal overhead compared to TDM. The introduced solution does not require modification of routers and therefore can be used together with any architecture utilizing non-blocking routers. The demonstration followed on the IDAMC platform, closely related to SoCRocket from WP4. However, the proposed methodology is universal and can be applied to the majority of the NoC-based multi- and many-core systems. Safety of the mechanism must be confirmed with tools for the formal verification of the worst-case behavior e.g. endto-end latency. Introduced efficiency drives new platform specific solutions which can be accompanied by domain specific tools for mapping, testing and deployment. The demonstrator was presented during the first review meeting in Munich, May 21-22, 2015.

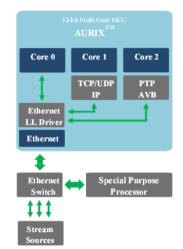

#### Multicore based communication platform (Infineon)

Infineon introduced in the scope of the task T3.2 mechanisms for the AURIX Microcontroller equipped with Ethernet connectivity. The main goal was to enable AURIX as a safe and efficient platform for mixed criticality

communication. The work concentrates mainly on the network layer form Figure 7.

Newsletterno, 4

*Figure 7: Infineon setup for the safe handling of mixed-critical communication*

The first period of work considered the evaluation of the Aurix platform, also in the scope of WP4. The system shown in Fig.3 offers high computing throughput and scalable performance, because it can process several tasks in parallel on different independent cores. Furthermore, AURIX offers a system to protect memory resources from accesses, which are unintended or malicious. As result the system can execute protected communication over several parallel "channels". These channels shall be separated due to the requirement that they can transfer information of different content and of different behavior profile. So Infineon introduced a solution using methods which support the freedom from interference between communication channels. Such solution was presented in a demonstrator.

Based on the analysis, the following extensions and mechanisms were implemented for RTEs:

- Isolation at application level

- Separation of message flows

- Isolation at stack level to enable deterministic behavior

Isolation at application level is achieved by putting the code images and the related data into different memory areas. Accesses to these areas are controlled and protected by AURIX HW. Separation as method is used in the demonstrator to build a secure environment for the applications in the multicore AURIX. The demonstrator

## Newsletter no. 4

supports the isolation at two levels: separation based on destination / source of the message flow and separation on the type of messages.

Consequently, the presented demonstrator introduces a setup which is able to isolate the message flows, using the HW protection mechanisms of the AURIX HW. The units build messages which are identical with the frames provided by the Ethernet protocol. The separation of the incoming message flow is the base for all isolation activities between messages. This is achieved using two decision units which must decide which type of messages has been received. In the demonstrator, two different targets can be addressed: TCP/UDP or AVB/PTP packages. The demonstrator was presented during the 1st consortium conference in Vienna, September 28,29 2015.

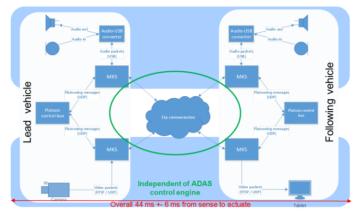

#### <u>Safety-critical wireless communication in platooning</u> (NXPNL)

NXPNL in T3.5 proposed a demonstrator considering the safety-critical application of wireless communication based on WiFi-p (IEEE 802.11p) in the platooning of commercial vehicles, see Figure 8 – off-chip networking technology. The solutions concentrates on the newtork and dynamic reconfiguration layers from Figure 5. Business-wise, platooning in the logistics market is forecasted to be an attractive segment in the adoption of automated driving and WiFi-p, whilst providing additional benefits in traffic efficiency, safety and fuel-economy / CO2 reduction. A consortium consisting of DAF, TNO, NXP Semiconductors and Ricardo realized a laterally automated platoon with headway distance of 0.5 sec (11m) @ 80 km/h, on the foundation of the Cohda Wireless MK5 On Board Unit empowered by NXP's RoadLINK dual-tuner chipset.

The custom-development on the MK5-based subsystem provides redundant and low latency platooning-controlinformation, bi-directional audio between the trucks and video see-through from 1st to 2nd truck, using multiple service channels in the licensed ITS band at 5.9 Ghz. In anticipation of possible future congestion in this band, a number of decentralized congestion control mechanisms as proposed in ETSI standards were investigated, simulated and prototyped. The system was demonstrated on the road in the EU Truck Platooning Challenge 2016, providing ample evidence of real-life performance and suggestions for future work. The demonstrator was also presented during the 2nd review meeting in Gothenburg, June 16-17, 2016.

Figure 8: Presented by NXPNL setup with WiFi-p subsystem with mixed criticality data-streams (4 antennas/channels offer redundant messaging, bi-directional audio and video, ETSI standards compliance, diagnostics and security)

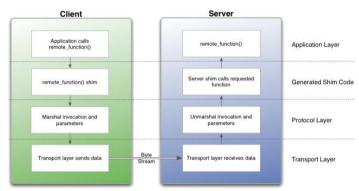

#### NXP/Freescale Embedded Remote Procedure Call (eRPC) Implementation

NXP/Freescale in T3.3 provides the cross-core Remote Procedure Call implementation as the base enablement software for many SoC platforms, including selected SoCs considered in WP4. The Embedded Remote Procedure Call (eRPC) library has been designed and implemented. The RPC is a mechanism used to invoke a software routine on a remote system via a simple local function call. When a remote function is called by the client, the function's parameters and an identifier for the called routine are marshalled (or serialized) into a stream of bytes. This byte stream is transported to the server through a communications channel (RPMsg elaborated in T3.2 task, or TPC/IP, UART, etc). The server unmarshalls the parameters, determines which function was invoked, and calls it. If the function returns a value, it is marshalled and sent back to the client.

RPC implementations typically use combination of a tool (eRPC generator) and IDL (interface definition language) file to generate source code to handle the details of marshalling a function's parameters and building the data stream. The tool also generates code for a server side shim that knows how to unmarshall a request and call the appropriate function. An IDL file is used to tell the generator tool about data types and RPC services.

The NXP/Freescale eRPC infrastructure offers:

- Multi-platforms: erpcgen tool is designed to be executable on most used operating systems (MacOS, Windows<sup>®</sup> OS, and Linux<sup>®</sup> OS).

- An easy way to create a client/server application.

- The server application can be blocking (when server serves only for client requests) or non-blocking (when server is executing also another code as the client requests).

- A simple changing transport layer (same applications can use a different transport medium).

Figure 9: NXP/FSL eRPC Layers

Main eRPC features:

- Lightweight but scalable, targeted to embedded systems

- Small generated code size to allow usage on multicore parts with small memory size

#### IV. AUTOMOTIVE APPLICATIONS WITH SERVICE ORIENTED ARCHITECTURE (SOA)

Jan van Deventer, LTU

One of the technologies of interest to EMC<sup>2</sup> is Service Oriented Architecture (SOA) and its integration in multi-core embedded systems used in applications with mixed criticality. This interest is driven by the promise that SOA components do not have to be fixed at design time, can evolve with time and can

begin to interact at runtime because they are loosely coupled and late binding. However, issues of security, dependability, interoperability and real time are also crucial to EMC<sup>2</sup> and are being

- Abstracted transport interface

- Serialization layer is abstracted and replaceable

- Small size of serialized data

- Designed to work well with C, but flexible enough to support object-oriented languages

Newsletterno, 4

- Asynchronous notifications from server to client

- Multithreading of servers when built with an RTOS

- Unique specification of a function to be called

- Provisions for matching response messages to request messages

- Versioning of services

- Minimize any latency impact

The first implementation has been done and available publically at GitHub:

#### https://github.com/EmbeddedRPC/erpc

A separate GitHub repository has been created to concentrate all guides for running NXP/Freescale multicore SW (eRPC, RPMsg/RPMsg-Lite) in heterogeneous multicore parts:

https://github.com/EmbeddedRPC/erpc-imx-demos

The demonstrator was presented during the 2nd consortium conference in Paris, September 27-28, 2016, showing the eRPC calls between Linux and FreeRTOS applications using the RPMsg transport layer.

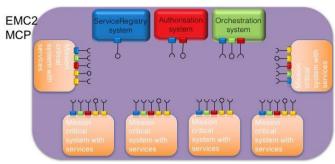

addressed in the project. Demonstrators are concrete instances of these concepts, two of which we present here.

They both use as a structure for the service oriented architecture the open source Arrowhead Framework [1]. This framework is the product of another Artemis Joint Undertaking project called Arrowhead. It requires only three core services while suggesting several other support services. The three core services are the registry service, the orchestration service and the authorization service. The first one, the service registry, keeps track of the services available. Its service discovery concept is similar to DNS and referred to as DNS-SD. The orchestration service provides the best service provider to the request of a service consumer that is looking for a specific service. The authorization service insures that the

## Newsletter no. 4

exchange of services is allowed. Together, they form a secure local cloud with low latency (Figure 10) [2].

Figure 10: Diagram of an Arrowhead Framework local cloud with its three core services and other application services

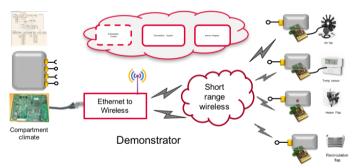

VOLVO and LTU have built a climate control demonstrator (Figure 11). A multi-core Xilinx Zynq development board holds the climate control service within an Arrowhead Framework local cloud. The development board communicates via Ethernet to a short-range wireless gateway on to wireless nodes. These nodes are a temperature sensor, an air blower and two ventilation duct flap servos. The services offered by the sensor and actuators are registered and discovered correctly. The demonstrator was shown at the EMC2 second review in Gothenburg and at the Artemis Technology Conference in Madrid of this year.

Figure 11: Multi-core ECU for climate control with SOA and wireless sensors and actuators

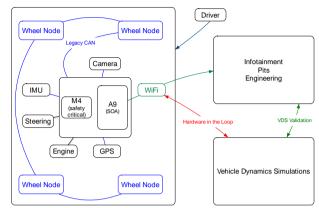

Students at Luleå University of Technology are developing another demonstrator: a car that has driveby-wire with active safety (i.e., ABS, electronic stability control (ESC)) and that can offer services, such as vehicle dynamics simulation validation over the Internet (Figure 12). To fit in EMC<sup>2</sup>, it has a main electronic control unit (ECU) with a multi-core embedded system. The car had I/O nodes at each wheel with a standard CAN bus to communicate over to the other nodes and the main ECU. These nodes are simple electronic control units and therefore are referred to as I/O nodes rather than ECUs. The car is, for safety and budget reasons, a 1/5 scale model car (Figure 13).

Figure 12: The drive-by-wire with active safety demonstrator concept

Figure 13: 1/5 scale model car with independent brakes

The actual implementation on the model car has a main ECU based on an NXP iMX6s SoloX with a heterogeneous multi-core processor containing a Cortex M4 and a Cortex A9. The I/O nodes are Cortex M0 produced by ST Electronics. The nodes broadcast CAN messages to the M4 and vice versa. The M4 and A9 communicate with each other via a messaging protocol called RPMSG (Remote Processor Messaging). The M0 nodes are interrupt driven and return to an idle state when no specific events need to be handled. They measure wheel speed, actuate the brake calipers via a servo motor. They also make the decision to reduce the brake torgue when the wheel tends to lock (distributed ABS). The M4 runs under real time operating system (Free RTOS) and handles the critical aspect of the system. The Cortex A9 runs Linux and offers SOA using the Arrowhead Framework.

Newsletter no. 4

Although taking other courses, the ten students were able to design and build the first hardware prototypes and software drivers to prove the concept within seven weeks. Rotating a wheel generates a wheel speed measured by the M0. This data is broadcasted to the M4, which further transmits it to the A9. The A9 offers this information as a service over Ethernet to a PC running the web browser Firefox with its Copper extension. The protocol used in this case is CoAP. The functional implementation was demonstrated to EMC<sup>2</sup> stakeholders on October 21, 2016. During the following eight weeks, they are to develop the application specific functions such as ABS and ESC. The vehicle states service will be used to validate or reject vehicle dynamics simulations performed in Adams Car using the ISO 19364 standard.

Although the automotive examples illustrate well the concepts of EMC<sup>2</sup> and SOA, they more importantly provide platforms where the EMC<sup>2</sup> partners can discuss and argue their own paradigms of Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real-time environments. An example of such discussion is: should the levels of criticality be on differrent cores or could they be found on the same cores? The model car implementation separates criticality levels on different cores: safety critical aspect on the M4 and non-safety critical aspect on the A9. A variation could move the Inertial Measurement Unit (IMU) needed for ESC from the M4 to the A9 where it would be offered as an IMU SOA service to the M4. From an EMC<sup>2</sup> point of view, that means that there would be mixed criticality on a single core, which awakes real-time and dependability discussions. Application wise, this refinement would allow the testing of the unmodified active safety software on the target hardware (M0 and M4) in a

#### V. EMC<sup>2</sup> USE CASE "HIGHLY AUTOMATED DRIVING"

This article is about a system architecture that exploits the potential of existing technologies around highly automated driving, which has been developed in task 2 of WP7. Preventing accidents and automating tasks in progressively

Raul Correal, IXION

hardware-in-the loop simulation using the actual vehicle as a service provider.

Nowadays it is easy to find real life examples where cars connected to the Internet have their control taken over by hackers. Since the model car's A9 is connect to the Internet, one should ask if hardware authentication and the Arrowhead Framework authentication are able to protect against that. To enhance this, the Arrowhead Framework has, with its concept of Local Cloud, a Gate Keeper service. When it comes to interoperability, the Orchestration service transparently invokes a protocol translator (e.g., CoAP-HTTP) between service providers and consumers. Dependability is another issue of interest. At the EMC<sup>2</sup>'s second review in June 2016, Virtual Vehicle demonstrated how dependable SOA (dSOA) could intervene when a sensor malfunctioned and the SOA system took over to correct for that. Their demonstrator was implemented on an Infineon's AURIX microcontroller using the Robotic Operating System (ROS).

EMC<sup>2</sup> is addressing relevant issues with SOA. Having concrete examples enables the illustration of the concepts as well as to foster discussions about how SOA on multi-core embedded systems with mixed criticality could be implemented.

- IoT Automation Arrowhead Framework, Delsing J. Ed., CRC Press Feb 2017.

- [2] Delsing J., Eliasson J., van Deventer J., Derhamy H., Varga P., Enabling IoT Automation Using Local Clouds, 2016 IEEE 3rd World Forum on Internet of Things (WF-IoT), Reston, USA, Dec, 2016.

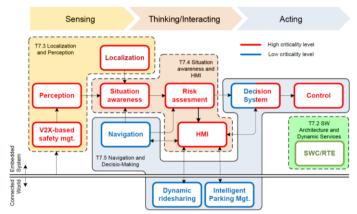

more complex driving situations requires innovation in perceiving the environment, the vehicle-state, and the reasoning about them. This can be done by the use of multiple sensor technologies such as radar, computer vision, LIDAR or even ultrasound, complementing and reinforcing each other, and communicating over a high bandwidth reliable network. The optimal use of such a huge amount of heterogeneous information requires innovations in both the involved component technologies and in the system architecture concepts. It is then

## Newsletter no. 4

mandatory to propose tailored solutions that take into consideration the heavy computational load imposed by such systems, and to adaptively combine it with the existing and upcoming platforms to significantly reduce the number of ECUs that would otherwise be required.

Mixed criticality management in automotive embedded systems is one of the hottest topics in the field. Thus, a commercial vehicle include nowadays a platform for time-critical embedded control-units (engine control, ADAS, highly automated vehicles), a platform for entertainment (navigation and multimedia) and even a platform for smart phones communication. In a parallel line, the progress in standalone and cooperative control systems towards highly automated vehicles is becoming a reality in experimental prototypes. It is then necessary to provide adapted dependable solutions that take into consideration the heavy computational payload of such systems and adaptively combine them with the existing platforms.

The main objective of this work is to investigate, implement and evaluate a system architecture that best exploits the potential of existing technologies around highly automated driving. To that end, the EMC2 architecture and tools enable the scheduling of timeand time-critical high-performance critical less functionalities on the same system, tested in real driving scenarios. This work goes beyond the state of the art in communicating ADAS and Highly Automated Vehicles through the design, development and validation of a solution optimizing the HW/SW resources of the multicore embedded cloud proposed in EMC<sup>2</sup>.

To that end, an urban commuting scenario has been identified, where safety for driver/passengers and predictability for other road users have to be guaranteed. Vehicles travel along the same roads around the same time of the day in a daily basis throughout the year. Often trajectories involve travelling from small roads within the rural and peri-urban area towards peri-urban agglomerations, which implies in many cases both merging to major roads and overtaking other vehicles.

In this use case the commuting vehicle is driven in a manual manner in a first stage. During this process, the embedded software learns the vehicle behavior and simultaneously localizes and builds a navigable map for autonomous navigation. When enough experience is acquired, the vehicle can inform the driver that it is now ready to drive autonomously in a second stage. When driving autonomously under the supervision of the human driver, the vehicle continuously monitors the integrity of the information provided by its sensors. In case of loss of integrity, it informs the driver that confidence is not high enough to continue to drive autonomously. In this case, an adapted HMI would suggest the driver to take-over control of the vehicle. In this context, if either some sort of functional mismatch is detected by the system and the driver prefers not to take-over or the driver simply feels sick, a stop over a safe location is automatically performed. The decision system is in charge of guaranteeing that the man-tomachine transition is secure, in the first case, and of guaranteeing smoothness and safety in the automated vehicle maneuver.

Figure 14: Functional architecture of the highly automated driving urban commuting use case

Vehicles which merge do so by finding the proper slot in the flow of vehicles on the major road. Once merged in the traffic, the automated vehicle reproduces the learned behavior if it is alone on its lane; otherwise it regulates its inter-distance with the vehicle in front of it. Besides, overtaking may be necessary if a vehicle is accidentally stopped in the middle of the lane or if it is just running too slowly for the cruise speed of our vehicle. It has been shown that both automatic merging and overtaking can be facilitated through the use of embedded V2X communications technologies.

The objective of this work has been therefore to use  $EMC^2$  architectures and tools in real-life tests, using current advanced sensing, navigation and co-operation

## Newsletter no. 4

functionalities for highly automated vehicles. Both simulation and real-life experiments have been made to show the potential of multi-core new service oriented architectures in the context of highly automated and connected driving. As a result of this, significant contributions with real-life experiments have been made in this still immature but promising field.

The proposed novel architecture of EMC<sup>2</sup> finds a solution to the fact that the increasing number of ECUs is hardly sustainable. Additionally, a key issue for driver acceptance and quick market introduction of such real time complex controlled systems is to assess its performance under uncertainty. In this connection, new functional safety and integrity requirements are appearing (ISO 26262).

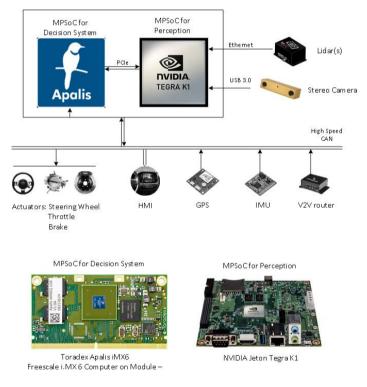

Figure 15: HW architecture of the MPSoC for UC T7.2

In consequence, the main objective of this work is to use EMC<sup>2</sup> architectures and tools in real-life tests, where a highly integrated computing unit has been developed, using current advanced sensing, navigation, decision making and cooperative functionalities for highly automated vehicles. The resultant design includes a SW architecture enabling the implementation of efficient algorithms in multi-core environments while preserving a high level of safety and reliability.

More specifically, multiple existing systems with different characteristics in terms of computational cost, control cycle period, or level of criticality (ISO 26262, IEC 61508) have been integrated. As a result, (i) an increased integration along with a (ii) consistent separation are natural requirements for the resulting mixed criticality runtime environments.

- Increased integration: Highly intensive computational components such as perception, map-based localization, decision making and V2X communications have been integrated in a reduced set of computing platforms, using a hybrid combination of different technologies within the same HW platform. The existing set of verification & validation artefacts for isolated components have been exploited for the resulting configuration in order to reduce V&V costs and efforts.

- Separation: One of the objectives for a mixedcriticality solution is to provide sufficient separation between elements of differing criticality levels to guarantee that the lower criticality elements cannot interfere with the functioning of the higher criticality elements. In particular, navigation related SW components have a lower criticality than most of the embedded subsystems. However, there are some specific components that combine high and low critical systems (namely, the decision system, which includes a time-critical motion planner, and a learning process that can be handled with a much lower criticality). System fault tolerance and resources requirements at local level have been taken into consideration with modelling approaches.

## Newsletter no. 4

#### VI. EMC<sup>2</sup> USE CASE: "DESIGN AND VALIDATION OF NEXT GENERATION HYBRID POWERTRAIN"

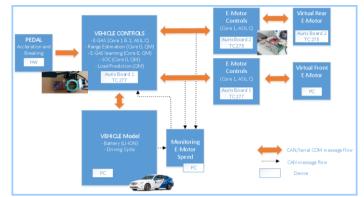

In the automotive domain current premium conventional and electric vehicles are characterized by several tens of distributed control units (more than 90 electronic control units with close to 1 Gigabyte software code [1]), with a complexity level of the E/E architecture significantly constraining vehicle performance improvements. Nevertheless, these

Georg Macher, AVL

systems are responsible for 25% of vehicle costs and an added value between 40% and 75% [2].

To achieve further benefits a further enhancement of the control functions and re-design of the current E/E architectures will soon be required. High-performance domain controller based on multi-core systems enable the deployment of more advanced control strategies providing additional benefits for the customer and environment, but at the same time the higher degree of integration and criticality of these control application raise new challenges. These factors cause multiple cross-domain collaborations and interactions in the face of the challenge to master the increased complexity and ensure consistency of the development along the entire product life cycle.

Consequently, UC7.3 focuses on enhancement and adaptation of vehicle electric / electronic architecture to better suit (a) the requirements coming from new applications fields such as higher degree of electrification and hybridization driving, and (b) opportunities coming from SOA approaches. UC7.3 provides an integration platform for technologies developed in the other WPs. The generic automotive E/E board net platform enables (a) the integration of new architecture concepts such as Service-Oriented Architecture (SOA), and (b) provides an integration platform to evaluate the outcomes from the different other WPs in a realistic environment.

Figure 16: Generic automotive E/E board net demonstrator

The generic automotive board net demonstrator provides the basis for independent and mixed-critical SW application integration on multi-core computing platform and integration of 4 independent SW stacks from different SW supplies, as demonstrated at 2nd year review meeting.

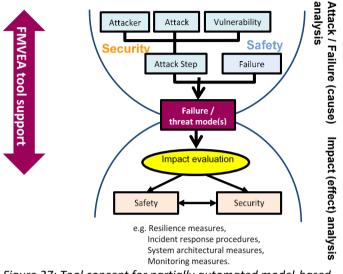

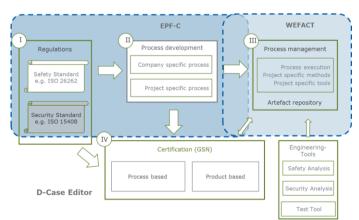

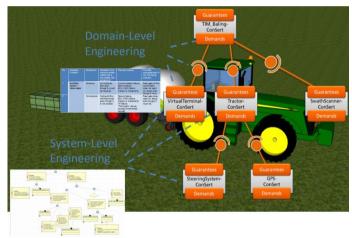

Beside the generic E/E architecture demonstrator, UC7.3 also focuses on dependability aspects, safety and security. An integrated dependability framework for providing product and process based safety and security argumentation, as well as, a contract-based approach for conditional safety certificates (M2C2 demonstrator) are integral part of UC7.3.

Figure 17: Integrated dependability framework.

This framework provides a comprehensive framework for safety & cybersecurity co-engineering, especially addressing the following aspects: (a) safety & cybersecurity assurance cases with the capability to generate and efficiently manage dependability information along the development lifecycle and (b) new safety and security concepts and their respective implementations. Thus, the

## Newsletter no. 4

framework shall help to ensure an efficient use of the components and E/E infrastructure and finally develop advanced and dependable control strategies for the end user.

Nevertheless, future needs of vehicle development rise the need for service-oriented architectures and dynamic reconfigurations. The dynamic compositions and reconfigurations (due to web-based functionalities and update-over-the-air functions) of these systems hamper the use of established engineering approaches, which cannot be applied without further ado. Current approaches assume, that a system as well as its usage context is completely known and can thus be analyzed thoroughly at development time, which does no longer hold true.

As a result, a shift of parts of the safety certification activities to runtime, where the complete information can be obtained and uncertainty can be truly resolved, is focused for the remaining project duration. The idea behind M2C2 contracts, a safety certification, which are created at development time, but evaluated at runtime by the systems themselves will be integrated in the UC7.3 demonstrator. This will merge all activities of UC7.3 for the final project review.

The efforts of UC7.3 allowed supporting a generic automotive board net demonstrator, which enables the coaching of SW developers (industrial engineers and scientists) for multi-core constraints, mixed-critical SW application integration and different SW supplier alignment. Furthermore, the integrated dependability framework invests ensure to further coalesce SW and safety engineering and strengthen the integration of these engineering domains.

- Christof Ebert and Capers Jones. Embedded Software: Facts, Figures, and Future. IEEE Computer Society, 0018-9162/09:42-52, 2009.

- [2] Giorgio Scuro. Automotive industry Innovation driven by electronics. <u>http://embeddedcomputing.com/articles/automotive-industryinnovationdriven-electronics/</u>, 2012.

#### VII. COTS MULTICORES IN AVIONIC APPLICATIONS

Sascha Uhrig, Airbus

Gerhard Fohler (TUKL)

Johannes Freitag, Airbus

Ankit Agrawal (TUKL)

Emerging safety-critical hard real-time systems like UAVs or autonomous driving applications require integration of many new functionalities. For example, in the future, autonomous helicopters (and autonomous aerial vehicles like air ambulances) targeting the urban city environment need to fly at low altitudes especially when picking-up or dropping-off either people or shipments. Implementation of such emerging applications requires even more performance from avionics hardware, without increasing or even better decreasing size, weight and power (SWaP). These requirements cannot be fulfilled by existing avionics hardware that use current avionics single-core processors.

COTS multicores can provide the requested limitations on SWaP as well as the requested performance, but introduce resource contentions on co-executing tasks due to sharing of hardware resources like on-chip network, memory sub-system etc. These shared resources result in timing dependencies amongst tasks leading to non-determinism of their execution time, i.e. tasks may not meet their deadlines. This behaviour can cause a serious safety issue on avionics systems. The CAST-32 position paper [1], jointly from EASA and FAA, further highlights the severity of the problem and as a first step, proposes to limit the number of active cores to just two.

## Newsletter no. 4

A naive solution is to use COTS multicore processors with only a single active core and keep all other cores either power down or idle. This results in waste of resources, while also defeating the purpose of increasing performance with the same SWaP. Solving the contention problem on COTS multicores requires an integrated approach combining contention-aware scheduling of applications and mechanisms that ensure bounded interference in COTS multicores.

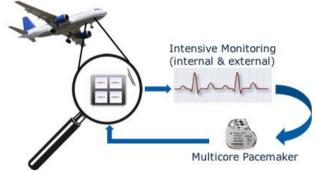

Figure 18: Overview of the methods developed in WP8.2

In WP8.2 of the EMC<sup>2</sup> project, we developed two methods adhering to the integrated approach, a runtime monitoring method and a static/dynamic scheduling method. For the runtime monitoring, a single critical core of a COTS multicore sends continuously data of the task's progress to an external safety-net processor (possibly DAL-A certified). The external processor comprises a database of performance fingerprints. Based on the executing task and the performance fingerprints it decides if the executing task is on time and will meet its deadline. If a delay is recognized one or more of the noncritical cores will be temporarily suspended or at least slowed down. This gives the critical core the possibility to speed-up execution and to keep its deadline anyway.

The second method allows using all cores in a COTS multicore as critical cores. For each fixed time interval called slot, each core executes tasks based on a schedule table. In each slot, if any task exceeds its assigned time budget and memory access budget, it may result in other co-executing tasks missing their deadlines. Therefore, the core-level scheduler suspends tasks that exhaust their budget reservations, until the start of the next slot. This case of possible runtime suspension is already accounted for in the offline scheduling phase, thereby enabling

concurrent execution of critical tasks on more than one core.

Currently, no mixed-criticality (DAL A-E) multicore application in avionics is known, as no COTS multicore has been certified for multi-application use. The blackbox nature of COTS multicore architectures combined with the lack of usage data impedes the use of COTS multicores in safety-critical avionics (e.g. DAL A). One way to overcome this issue is to use COTS multicores for lower-criticality applications like DAL C-E, and collect inflight experiences. This data can then aid in certification of COTS multicores in avionics for DAL A/B applications [2]. The static/dynamic scheduling and the monitoring methods, can aid in this direction as they complement each other and it is possible to combine them. The monitoring method can be coupled with an underlying static/dynamic scheduling and act as an additional layer to ensure that the COTS multicore is executing tasks as intended. In case of any abnormality, the external processor can either take mitigating actions or simply inform the other nodes in the system and log the incident.

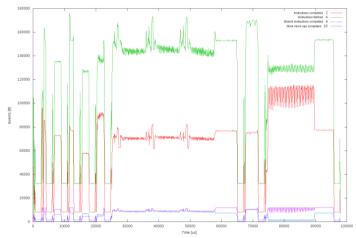

Figure 19: Example fingerprint of a benchmark application

The monitoring method is implemented for a DAL-C application inside an avionics computer. Inside the FPGA a safety net processor is tracking the application executed on the dual-core NXP P5020 processor. An example fingerprint of a benchmark application is shown in Figure 19. The different characteristics of the application's progress can be identified easily. In summary, the presented methods have the potential to pave way for use of COTS multicores in safety-critical domains like

Newsletter no. 4

avionics, such that tasks are executed deterministically considering resource contentions.

#### VIII. FPGA PARTIAL RECONFIGURATION IN SPACE APPLICATIONS

Elena Terradillos, Tecnalia

Manuel Sanchez TASE

Within the MPSoC Hardware for Space use case in EMC<sup>2</sup> WP9, TECNALIA and TASE work together to provide a solution so that partial reconfiguration of programmable devices can be done in a reliable way in the space environment. The target programmable devices are SRAM-based FPGAs and, in particular, the Xilinx Virtex-5QV FPGA which is the highest density and performance space-grade FPGA in the market built with radiation-hardened by design technology to provide intrinsic hardness from SEU (Single Event Upset) and SET (Single Event Transient) to select elements of the device.

SRAM-based FPGAs have become increasingly attractive for space-based computing platforms due to: (1) their onorbit re-configurability which extends the useful lifetime of the system; (2) their low development cost comparing to ASICs; and (3) they are well-suited to digital signal processing tasks, which are very common in satellite applications. Unfortunately, these devices are susceptible to SEUs which can make fault-tolerant implementations challenging, but not impossible. The Xilinx Virtex-5QV device was rolled out in 2011 and there are many NASA missions with Virtex-5QV programmed to be launched on 2017 and beyond.

If FPGA technology provides the flexibility of modifying a design by re-programming without going through re-

- [1] CAST-32 Multi-core Processors. FAA's Certification Authorities Software Team, May 2014.

- [2] R. Fuchsen, "How to address certification for multicore based IMA platforms: Current status and potential solutions," 2016.

fabrication, Partial Reconfiguration (PR) takes this flexibility one step further. PR is the ability to dynamically modify blocks of logic while the remaining logic continues to operate without interruption. It allows designers to change functionality on the fly, eliminating the need to fully reconfigure and re-establish links. This technique presents several advantages: (1) reduce the size of the FPGA device required to implement a given function, with consequent reductions in cost and power consumption; (2) provide flexibility in the choices of algorithms or protocols available to an application; (3) enable new techniques in design security; (4) improve FPGA fault-tolerance; and (5) accelerate configurable computing.

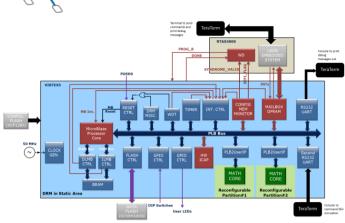

When designing an FPGA-based platform with partial reconfiguration for mixed-criticality systems, there are three elements or key points to be included: a) a Dynamic Reconfiguration Manager (DRM) in the FPGA static partition; b) fault-tolerance elements and design techniques; and c) an external agent to control and monitor the DRM.

A Reliable and Self-Healing Dynamic Reconfiguration Manager is the proposed solution so that partial reconfiguration of a Xilinx Virtex-5QV FPGA can be done in a safe (reliable) way in the space environment. This DRM consists in a MicroBlaze embedded system implemented in the static (that is, not reconfigurable) area of the Virtex-5 device with capability to manage the reprogramming process of several reconfigurable partitions. The DRM is a co-processor of the full system. One of its main elements is the controller to access the FPGA configuration memory at run time (HW ICAP). This capability to access the FPGA configuration memory is used for a double purpose: first, to perform dynamic reconfiguration of the reconfigurable partitions; second, to perform configuration memory scrubbing in order to prevent SEU accumulation in the FPGA configuration memory.

## Newsletter no. 4

Figure 20: Reliable and Self-Healing DRM architecture diagram Fault-tolerance elements and design techniques are included so that the DRM can autonomously recover from radiation induced errors. These elements and techniques are:

- FPGA configuration memory management. SRAMbased FPGAs are sensitive to SEUs affecting the configuration memory. This is especially challenging as these upsets may change the behaviour of the FPGA design. Taking actions to mitigate the effects of SEUs in the configuration memory is essential for reliable SRAM-based FPGAs in the space environment and critical systems in general. This task is performed by the MicroBlaze microprocessor with the support of the Configuration Memory Monitor peripheral.

- SEFI detection mitigation. and Single-Event • Functional Interrupts (SEFIs) are SEUs that result in the interference of the normal operation of a complex digital circuit. For example: an SEU in the device control circuitry may place the device into a test mode, halt, or undefined state; or the so-called sequence loss in processors resulting, for instance, of an SEU in the program counter leading to an infinite loop. In general, SEFI is a broad term used to indicate a failure in a support circuit within the device and not a failure of the user design. In such cases, a reset of the application or a power off/on cycle is required to recover the full functionality of the system. The external monitor agent forces full Virtex-5 reprogramming when SEFI conditions are detected.

- MicroBlaze soft-core protection. It consists in enabling the MicroBlaze fault-tolerance features to detect errors in the processor memory and perform the corresponding correction actions.

- Partial reconfiguration data integrity check. The purpose of this technique is to avoid loading a corrupted partial bitstream.

- The EDAC (Error Detection And Correction) circuit of the RAM blocks is enabled in the whole design, both the embedded system in the static partition and the designs in the reconfigurable partitions. The SET filters of the CLB flip-flops in the Virtex-5QV FPGA will also be enabled.

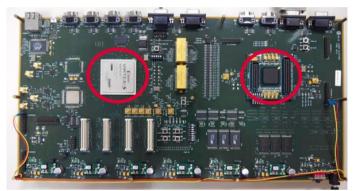

The DRM has been designed to be implemented in the Virtex-5 device of the LADAP (L3SoC and Data Processing) platform developed by TASE. The two main elements of this hardware platform are: the already mentioned Xilinx Virtex-5 device, and a Microsemi ProASIC FPGA that will include the main processor of the system.

Figure 21: LADAP platform

The DRM is externally controlled and monitored by the LEON processor running in the ProASIC device. The communication interface between both processors has been devised as a mailbox implemented in a shared dual port memory in the Virtex-5 FPGA. The LEON processor is always the communication master. It periodically checks that the DRM is alive and commands the partial reconfiguration actions. Together with a watchdog module, it reprograms the Virtex-5 FPGA when SEFI conditions are detected.

During the EMC<sup>2</sup> second year review, a demonstration video showing partial reconfiguration working in the Virtex-5 FPGA under command of LEON processor was presented. The fault-tolerance elements have been implemented afterwards and their functional validation is in progress. Autonomous fault recovery of the system will be demonstrated in the final review.

## Newsletter no. 4

#### IX. EMC<sup>2</sup> "INTERNET OF THINGS" USE CASES

Yudani Riobó, Quobis

Internet of Things (IoT) defines a scenario where everyday physical objects are connected to the Internet and interoperate with other objects and systems. The challenge relies on the higher computing resources needed to process the increased amount of data available, as

well as safety and security issues in open and dynamic environments. The Internet of Thing living lab focuses in different scenarios to develop new functionalities and improvements. It includes a number of use cases that are providing some interesting results.

#### Deterministic network of cameras

One of the use cases aims to showcase the potential of open deterministic networking by connecting a variety of local embedded systems to other embedded systems. Open deterministic networks are an enabling technology for future, potentially heterogeneous and mixedcriticality, Systems-of-systems (SoS). There, distributed components or systems will be connected and integrated towards larger systems, while their individual requirements, e.g. regarding safety parameters, are preserved by the novel networking infrastructures.

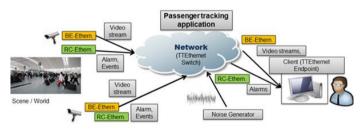

The first prototype demonstrates a novel approach for monitoring people on airports and measuring passenger data by interconnecting cameras, server and client in a deterministic communication network.

*Figure 22: Measuring waiting time by utilising a deterministic network of cameras, server and client*

The person tracking application and the additional middleware, both developed in living lab WP12, is used to implement server side the demonstrator's passenger monitoring. Cameras and client are specifically connected via TTEthernet for streaming video data and server side generated events to the client.

The demonstrator provides two different modes of communication namely rate-constrained (RC) and besteffort (BE) communication. The event data including specific alarms are transmitted via the rate-constrained mode as this communication guarantees a maximum delay of one Ethernet frame or packet, if there is one RC link out the specific port. If many RC links are to be sent out the same port (client), then the frame might be delayed longer (first come, first served). A delay of a few Ethernet frames is more than acceptable for the proposed application, so that the third time-triggered mode that guarantees to transmit data without almost any delay is not needed. The server is periodically transmitting the event data to the client. It contains the current on average waiting time monitored by each camera and eventual alarm messages for example when on average waiting time exceeds a user defined threshold. In this demonstrator, waiting time is the time a passenger is correctly tracked by the tracker application.

A noise generator has been connected to the network as well in order to simulate network overload. In such situations the demonstrator shows that event data in rate-constrained mode arrives correctly at the client whereas video directly streamed to the client under besteffort mode may show frame drops. Experiments verifies that deterministic network communication allows safe processing of video and safe event delivery at the client side which is a necessary prerequisite when putting cameras into the control loop of the gate process.

#### Synchronized low-latency deterministic networks

This use case aims to increase the dependability on communication networks for Smart Grid, focusing on availability, safety, security and reliability. Control, monitoring and critical data rely on these features and thus, on synchronization. Timing data becomes crucial since it is required to provide properly the intercom-

Newsletter no. 4

nection between different grid elements and guarantee their functionalities. Next Smart Grid network generation lie on high-accurate, reliable, available and scalable technologies to distribute time. White Rabbit (WR) is intended to be the next-generation deterministic network based on synchronous Ethernet, allowing lowlatency deterministic packet routing and high precision for timing transmission. WR networks are composed by a master node that provides the main time and frequency reference, fibre switches, twisted-pair copper, and slave nodes.

WR allows a very precise time-tag data measurement and data triggering acquisition in large installations at the same time that data are also transmitted through the same network. The demonstrator of this use case addresses the development of a novel technology for Smart Grid control. In order to validate the design of this demonstrator two prototypes have been developed. The first prototype focuses on evaluating the scalability, synchronization accuracy and the utilization of different time distribution mechanisms, such as WR-PTP and IRIG-B. The second one focuses in assessing the robustness and availability of different services focusing on time distribution.

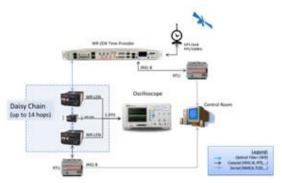

#### Accurate & heterogeneous time transfer system prototype

This prototype is composed of a WR-ZEN configured as a time provider connected to a GPS. The WR-LEN boards are connected in a Daisy Chain configuration with a modified White Rabbit PTP Core (WRPC) containing two endpoints.

Figure 23: Scalable heterogeneous time transfer system using WR-PTP and IRIG-B

This prototype integrates the project results regarding the determinism of the network architecture and the ones focusing on enhanced QoS definition for critical data packets as timing ones. This demonstrator illustrates the benefits and capabilities of the presented approach for Smart Grid. Benefits of this synchronized, low latency and deterministic networks as enabling technology for new applications or for improving development of existing ones will be shown.

#### High-availability and fault tolerance prototype

This prototype consists of a WR-ZEN configured as the Grand Master time provider, connected to a GPS, which disseminates time and frequency with 1ns accuracy to a HSR ring network composed of three WR-HSR-Switches. These switches are also synchronized to the WR-ZEN providing a 1-PPS signal perfectly synchronized to the GPS clock 1-PPS.

Time frames are propagated from the WR-ZEN to the first WR-HSR-Switch, where it will insert a HSR tag, duplicate and send both the frames through the ring to the other two WR-HSR-Switches. Each of the switches will receive two copies of the same time frame, making one of them the time reference, and the other one is used a backup in case of failure of the other ring path.

Figure 24: Time transfer fault tolerant system in HSR network

When one of the nodes or path is down, one of the time references is lost, and the switches shall switchover to the previously backup time reference. This is done with approximately zero-time recovery, feature required by Smart Grid high-demanding applications where timing is considered critical.

## Newsletter no. 4

#### X. EMC<sup>2</sup> USE CASE: "VIDEO SURVEILLANCE FOR CRITICAL INFRASTRUCTURE"

Axel Weißenfeld, AIT

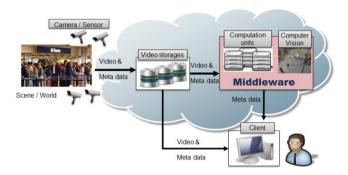

#### Passenger Tracking - Architecture for Dynamic Allocation of Computer Vision Tasks

This article is about an architecture for dynamic allocation of computer vision tasks, which has been developed in task 2 of WP12 and was presented at the International Conference on Distributed Smart Cameras 2016 (ICDSC).

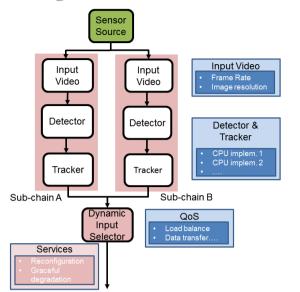

The use of reconfigurable computer vision architecture for real time image processing tasks is an important and challenging application in cyber-physical systems with limited resources. This architecture shall be used in WP 11.2 to realize a networked smart vision system using the TTEthernet technology from partner TTTech. This network supports mixed-criticality communication, thereby ensuring that high criticality communication will be guaranteed thereby using single communication networks. Thus, also low-criticality messages are sent over the same network.